Cysic: ZK 산업에서 zkVM는 어떻게 새로운 패러다임이 되는가? -(4)

CPU와 맞춤형 FPGA 기계를 결합한 접근 방식을 사용하여 상당한 진전을 이루었지만, 성능은 여전히 최종 목표인 실시간 ZK 증명과는 거리가 있습니다.

이러한 미흡한 성능은 Amdahl의 법칙과 다른 하드웨어 구성 요소 간의 상호 작용 비용 때문입니다. Amdahl의 법칙은 시스템의 단일 부분을 최적화하여 얻을 수 있는 전체 성능 향상이 제한적이라고 명시하고 있으며, 이는 다른 하드웨어 모듈 간의 통신 비용에 의해 더욱 악화됩니다(위키피디아에서). CPU에 비해 상당한 속도 향상을 달성하기 위해서는 단일 하드웨어에서 모든 가능한 구성 요소가 가속화되어야 합니다.

그러나 ZK 알고리즘의 다양성 때문에(명확히 말하자면, ZK 알고리즘은 ZK 증명 생성에서의 계산 작업을 가리킵니다) 이는 불가능한 것으로 보입니다. 예를 들어, 위의 트위터 스크린샷은 Poseidon Hash, EVM, GPT-2의 세 가지 ZK 회로를 보여주는데, 같은 증명 백엔드(Halo2-KZG)를 사용함에도 불구하고, 특히 증인 생성 부분에서 계산이 매우 다릅니다. 스크린샷은 또한 다른 증명 백엔드(예: Plonky2/3 및 Gnark)를 포함하고 있지 않습니다.

여기서 우리가 하고 싶은 말은 하드웨어가 ZK 알고리즘의 다양한 온칩 계산 작업을 수용할 수 있을 만큼 일반적이어야 한다는 것입니다.

FGPA-ASIC 하이브리드 아키텍처

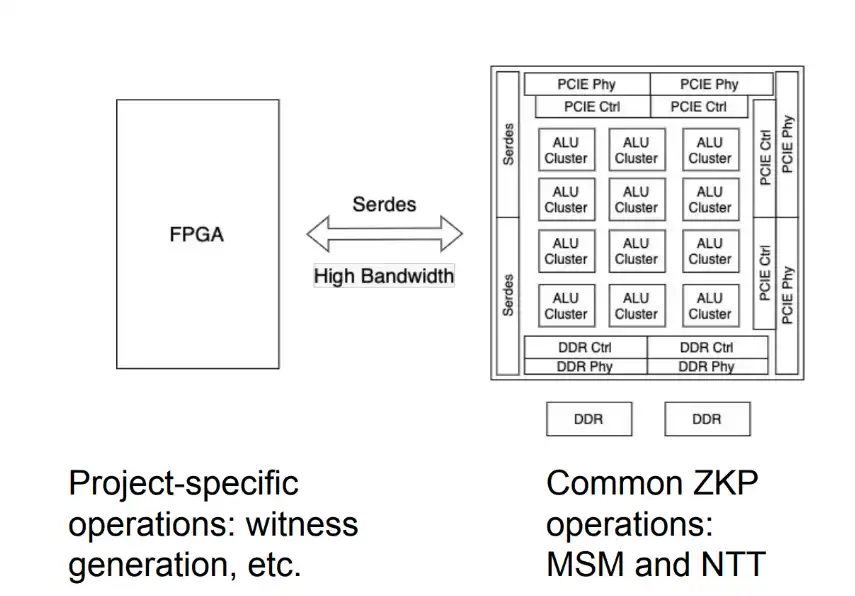

이 하이브리드 구조에서는 ASIC이 일반적인 작업을 수행하고 FPGA가 회로별 계산을 수행합니다. 두 하드웨어 장치는 동일한 PCB 보드에 장착되어 고대역폭 SerDes 채널을 통해 연결됩니다. 또한 RISC-V 또는 ARM 기반과 같은 온칩 CPU 코어도 유사한 목적으로 사용될 수 있습니다. 이러한 하이브리드 접근 방식은 일반적으로 비용과 제조 품질 측면에서 매우 높은 요구 사항을 가집니다. 지난 6개월 동안 우리는 스스로에게 물었습니다:

"하이브리드"가 우리가 생각할 수 있는 최선의 구조일까요? 우리는 ZK 커뮤니티의 기술적 진보에 의존하여 우리의 설계를 개선할 수 있을까요? 아래에서 우리는 위의 질문에 상당히 긍정적인 입장입니다.

영희에게 코인 인증하고 코인올백 심화방 입장하기